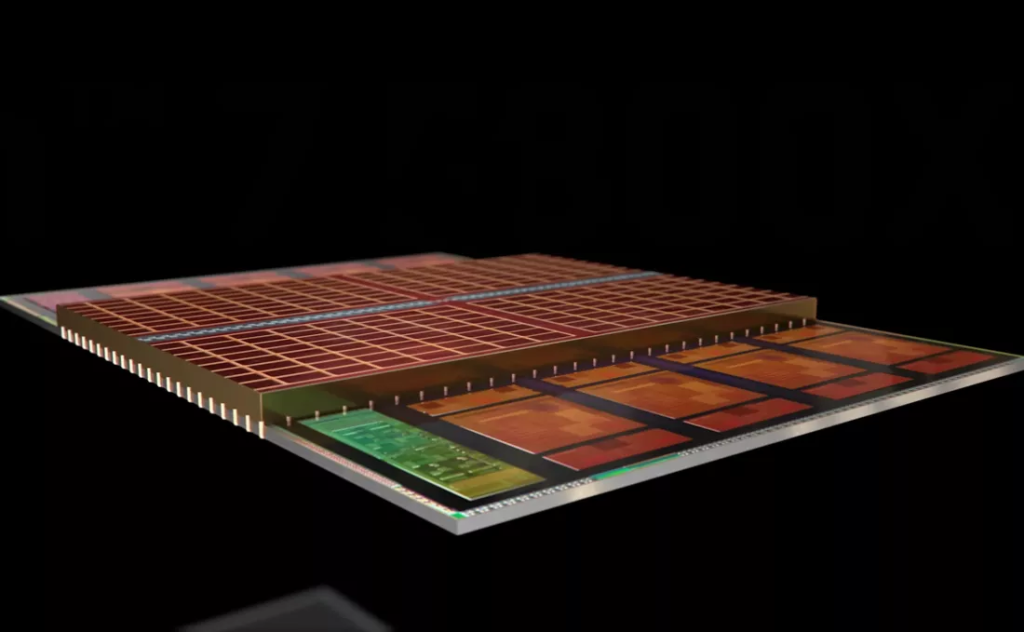

AMD a commencé à mélanger les nœuds en 2019 en utilisant le nœud de 7 nm pour le dé complexe du cœur (CCD) et le nœud de 12 nm pour le dé IO de la microarchitecture Zen 2. Récemment, AMD a confirmé à Tom’s Hardware que Zen 4 passerait à trois nœuds : le nœud de 5 nm pour le CCD, le nœud de 6 nm pour le dé IO et le nœud de 7 nm pour le V-Cache.

Lors de sa récente présentation à l’ISSCC, AMD a expliqué certains des défis qu’il a rencontrés en empilant un nœud sur un autre. Les V-Caches de la 7950X3D et de la 5800X3D originale sont positionnés au-dessus de leurs caches L3 ordinaires pour permettre leur connexion. Cette disposition permet également d’éloigner le V-Cache de la chaleur produite par les cœurs. Cependant, alors que le V-Cache s’adapte parfaitement au cache L3 dans le 5800X3D, il chevauche les caches L2 sur les bords des cœurs dans le 7950X3D.

Il y a plusieurs raisons qui expliquent le problème du V-Cache d’AMD. D’une part, AMD a doublé la quantité de cache L2 par cœur, passant de 0,5 Mo dans Zen 3 à 1 Mo dans Zen 4, ce qui a pris plus d’espace. Pour y remédier, AMD a percé des trous dans les caches L2 pour les traversées de silicium (TSV) qui alimentent le V-Cache, mais cela a créé d’autres défis. Les TSV de signal proviennent toujours du contrôleur situé au centre du CCD, mais AMD les a également modifiés pour réduire leur encombrement de 50 %.

Malgré ces contraintes, AMD a réussi à réduire la taille du V-Cache de 41 mm2 à 36 mm2 tout en conservant les 4,7 milliards transistors. Pour y parvenir, TSMC a fabriqué le cache sur une nouvelle version du nœud de 7 nm qu’il a développée spécialement pour la SRAM. Cela a permis au V-Cache d’avoir 32 % de transistors en plus par millimètre carré que le CCD, même s’il est fabriqué sur un nœud de 7 nm plus grand.

Ces modifications et améliorations ont entraîné une augmentation de 25 % de la bande passante, qui passe à 2,5 To/s, et une efficacité accrue. Ces résultats sont impressionnants compte tenu du délai relativement court entre la première et la deuxième génération d’un chiplet supplémentaire.